锁存器

复习

- 第九章:设计完成了减法器,本质是加上一个负数(补码)

- 第十章:设计完成了乘法器,本质是多次加法,也可以用 Booth 算法等进行优化

- 第十一章:设计完成了除法器,本质是移位和减法的组合

- 第十二章:利用上面的部件,制造了一个简单的 ALU(Arithmetic Logic Unit,算术逻辑单元)

- 第十三章:突发奇想将部件门首尾相连,观察到了“记忆”现象

TL;DR

- 锁存器由一些基础逻辑门组成,不同的是,他们之间有首尾连接的现象

- 锁存器是最简单的记忆单元

- 最简单的锁存器是 SR 锁存器,进阶锁存器是 D 锁存器

正文

锁存器:最简单的记忆电路

上一张我们看到了逻辑门首尾相连的“记忆”现象,那么如果逻辑门连接得多一些呢?能否形成一个记忆电路,进而控制写入和输出呢?

可以试一下。

AND-OR 锁存器

上面这个由 3 个逻辑门构成的最简单的锁存器,叫 and-or 锁存器,也叫 SR 锁存器(Set-Reset Latch)。

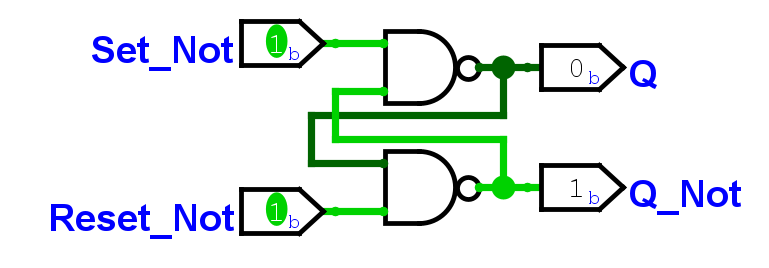

其实 SR 锁存器还有另一种电路图,逻辑门更少,但看起来更复杂,用 2 个与非门(nand)即可。

注意:下面图中输入的是 S 和 R 的反相,即 S’ 和 R’,也即当 S’ 为 0(实际上是 S = 1)时,将输出置为 1。输出同样有两个值,一个为 Q,另一个 Q_Not 为 Q 的反相。

看起来很晕对不对?所以为了保持简洁,之后还是使用上面的图,哪怕门多一点。当然,如果真要造 CPU 肯定是逻辑门越少越好,到时候必须使用下面的图了。这时候头脑必须时刻保持清醒。

输入

- S(Set):设置输出为 1,除非 Reset 改变

- R(Reset):将输出复位,设置为 0

真值表

| S | R | Q(下一状态) | 说明 |

|---|---|---|---|

| 0 | 0 | Q(保持) | 保持当前状态 |

| 0 | 1 | 0 | 复位 |

| 1 | 0 | 1 | 置位 |

| 1 | 1 | 不确定 | 禁止状态 |

思考题 1

为什么 S = 1,R = 1 的时候,Q 会变成不确定?

D 锁存器

用 Set 和 Reset 控制输出,感觉有些复杂,锁存器多起来之后很容易晕。

有没有什么办法,能使输入简明一些呢?比如是否启用锁存器(Enable)?

增加增加了两个与门,一个非门和两个输入:数据 D(Data) 及输入启用线 WE(Write Enable,或写为门控 G,Gate,等到有时钟时,也可写为时钟脉冲 CP,Clock Pulse,时钟脉冲会在 0 和 1 之间跳变,所以会每隔一段时间就可以写入)。

这种锁存器叫 D 锁存器,也叫门锁(因为门可以打开也可以关上)。

图看起来会有些绕,可以先不用往下看,先想一下。

真值表:

| D | WE | Q(下一状态) | 说明 |

|---|---|---|---|

| X(无关) | 0 | Q(保持) | 保持当前状态 |

| 0 | 1 | 0 | 置位 |

| 1 | 1 | 1 | 置位 |

思考题 2

继思考题 1,D 锁存器有输出不确定的禁止状态吗?

锁存器的问题

锁存器有一个问题:它对输入信号太敏感了。只要输入变化,输出就可能变化。复杂的电路中可能会导致混乱。

有什么办法解决这个问题呢?

小结

知识点

- SR 锁存器

- D 锁存器

思考题答案(仅供参考)

思考题 1

若 Q = 1,则 R = 1 应使其复位为 0;若 Q = 0,则 S = 1 应使其置位为 1。两种逻辑冲突导致电路无法稳定。

思考题 2

没有。可以看一下上面的动图,无论 D 和 WE 怎么变化,D 锁存器结构中 SR 锁存器的那两个输入,都不会出现同时为 1 的禁止情况。而 SR 锁存器仅在输入同时为 1 时才会出现输出不确定的禁止状态。

参考资料

推荐

协议

本作品采用知识共享署名-非商业性使用-相同方式共享 4.0 国际许可协议进行许可。

封面图

设计师 | 南国微雪